1

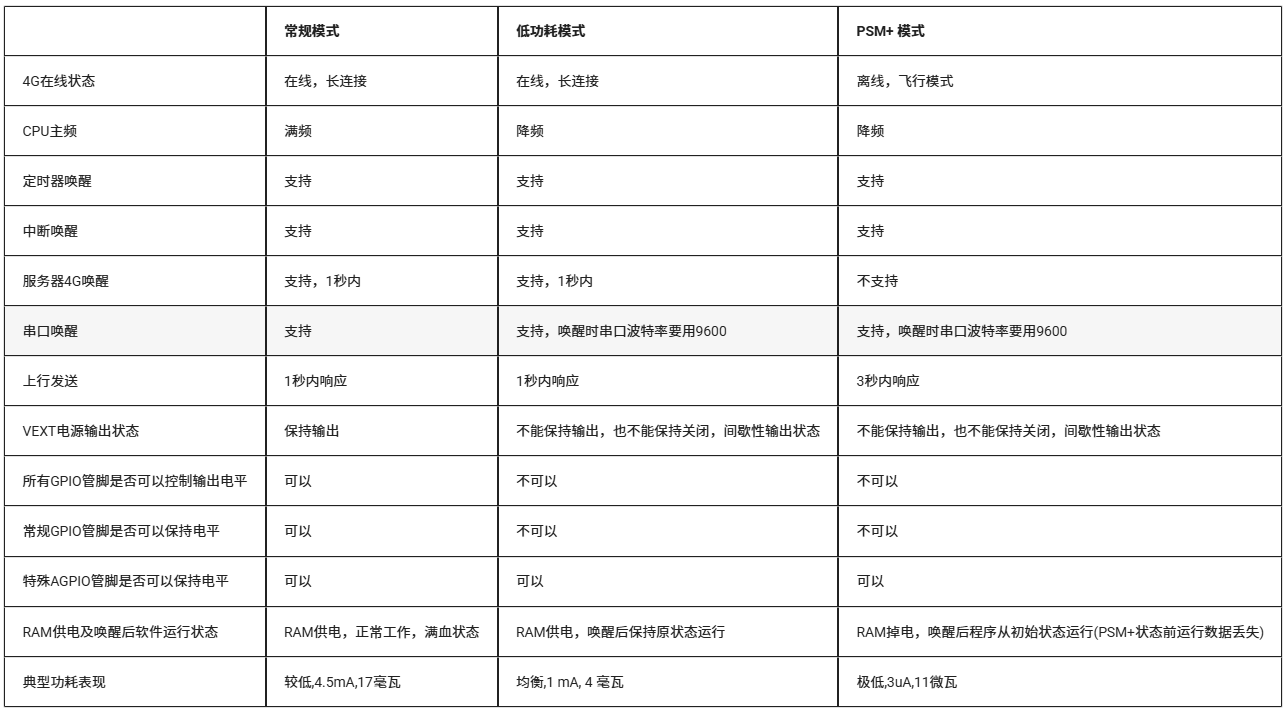

1.1.产品简介

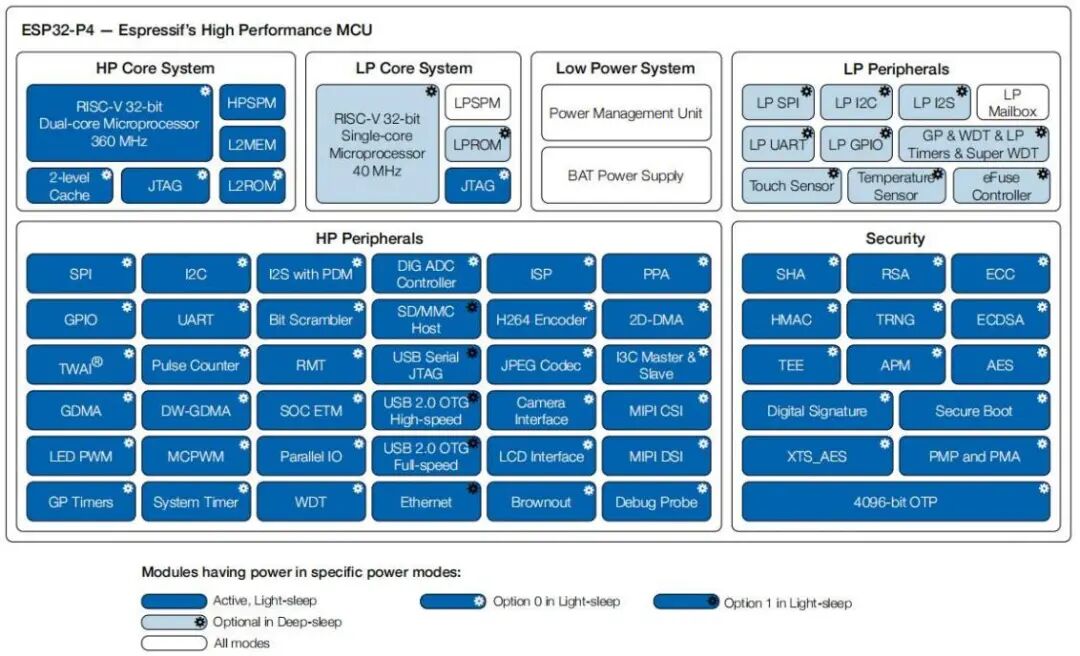

WT0132P4-A1 是深圳市启明云端有限公司推出的基于乐鑫 ESP32-P4 芯片设计的一款集成 NOR FLASH 小尺寸邮票孔核心板。核心处理器芯片 ESP32-P4 封装内可叠封 16MB 或 32MB PSRAM,包含 2 个高性能(HP)内核和一个低功耗(LP)内核。HP 内核采用 RISC-V 双核处理器,主频高达 360MHz,包含一个 JPEG 编/解码器、像素处理加速器、H.264 视频编码器和 MIPI 接口;具有强大的图像和语音处理能力。

图1:主芯片架构图

WT0132P4-A1 系列共两种规格,具体信息见下表。 WT0132P4-A1 系列型号对比:

2

产品特点

双核 360 MHz 高主频 CPU

内置 16 MB Flash 与 16/32 MB Psram

ESP32-P4 芯片全引脚引出

支持多个多媒体接口

核心板尺寸小,便于硬件设计

开发资料齐全

3

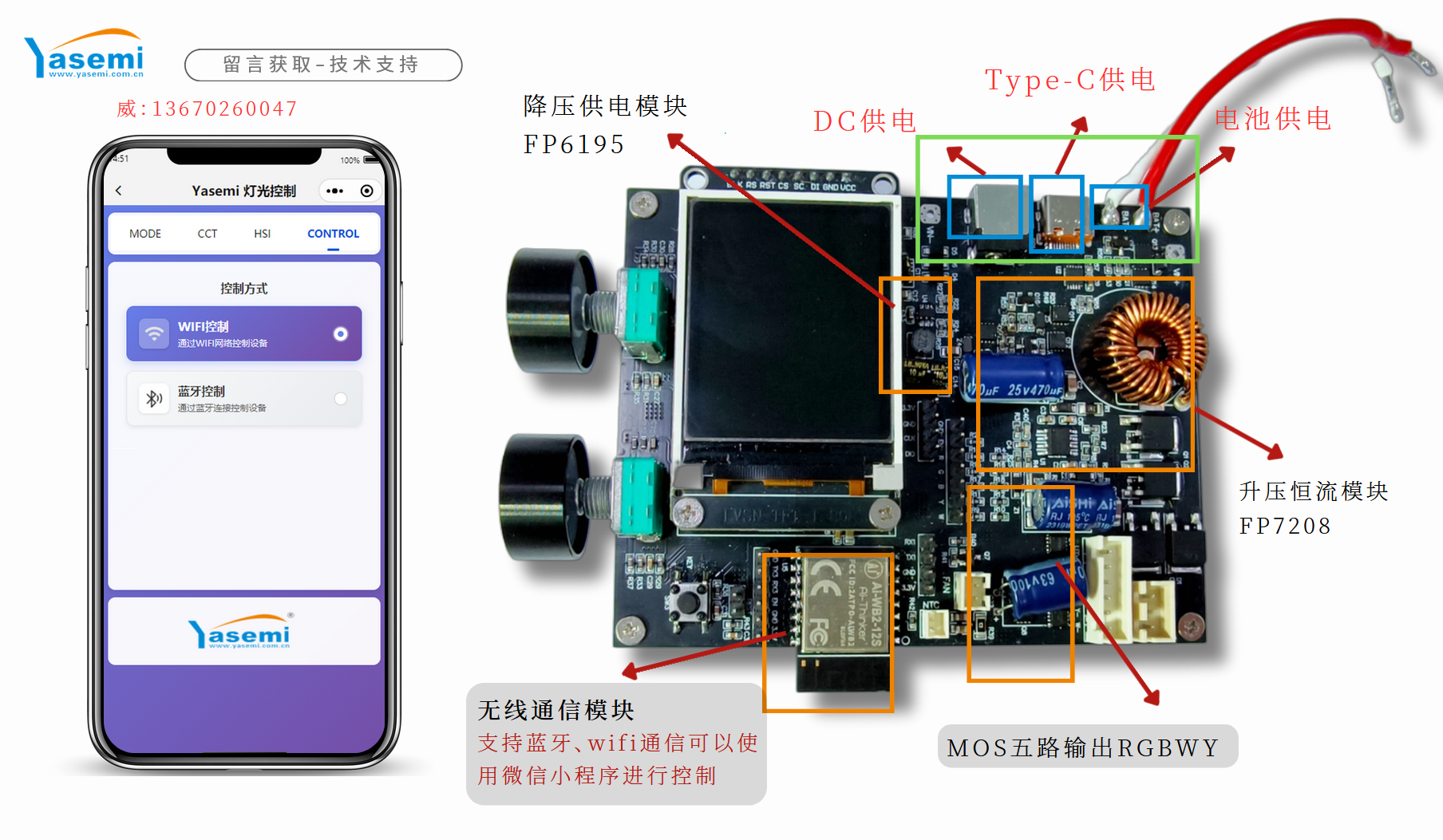

产品图片

图2

WT0132P4-A1-N16R16(正)

图3:

WT0132P4-A1-N16R16(背)

图4

WT0132P4-A1-N16R32(正)

图5:

WT0132P4-A1-N16R32(背)

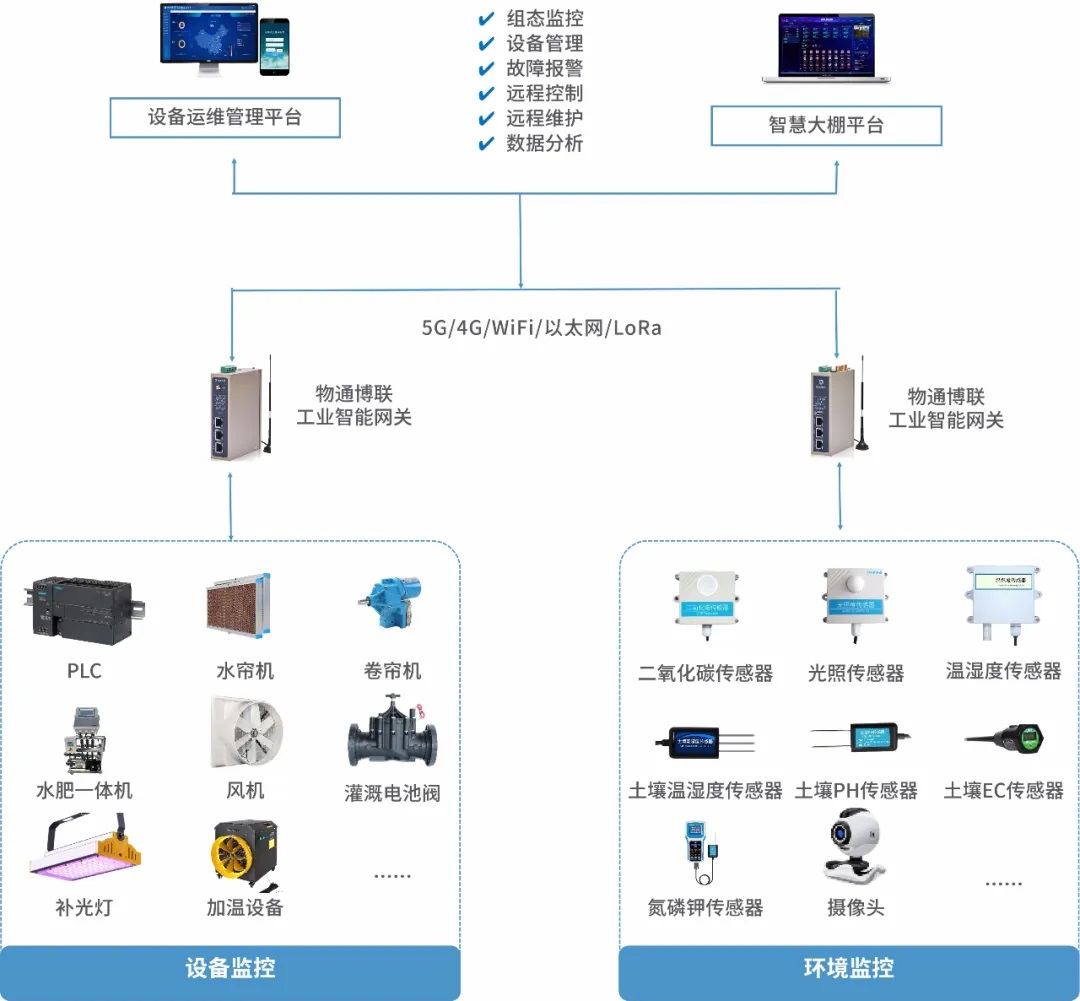

应用场景

智能家居

工业自动化

消费电子产品

HMI 人机交互

电子机器人

摄像头视频流传输

USB 设备

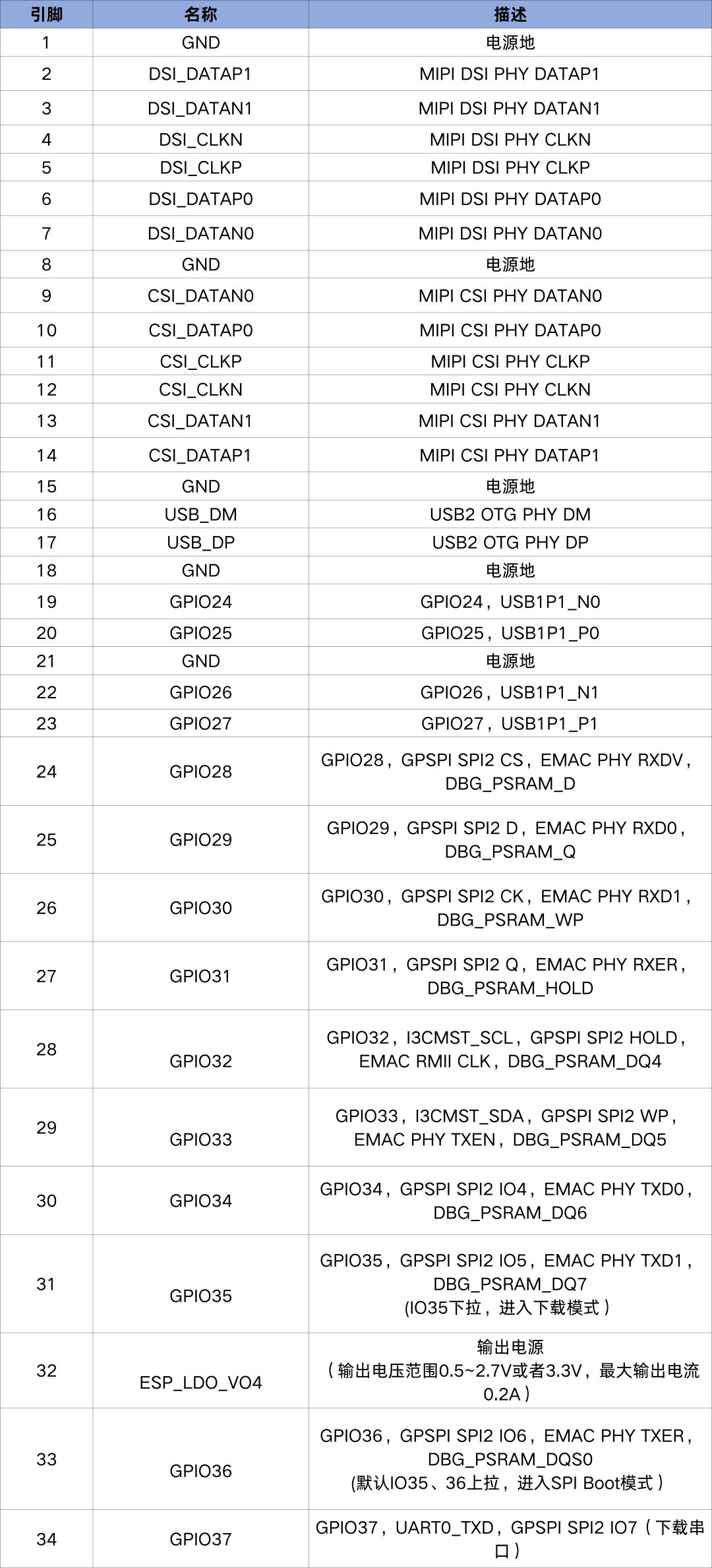

产品规格

1

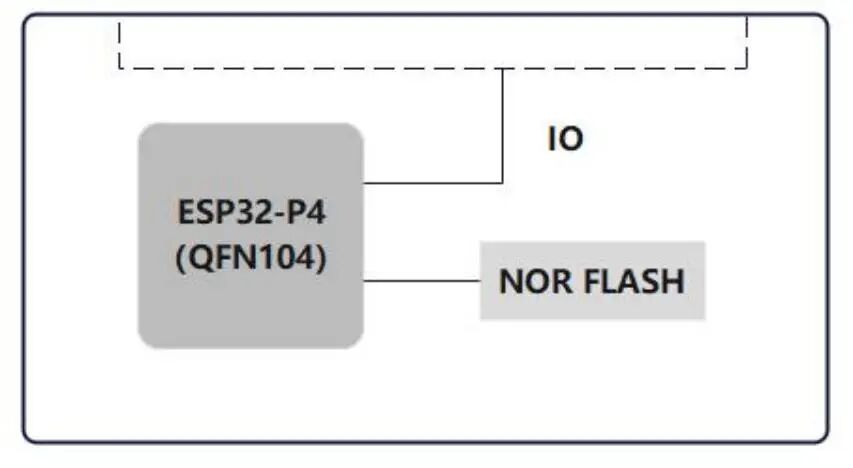

功能框图

图6:WT0132P4-A1 功能框图

2

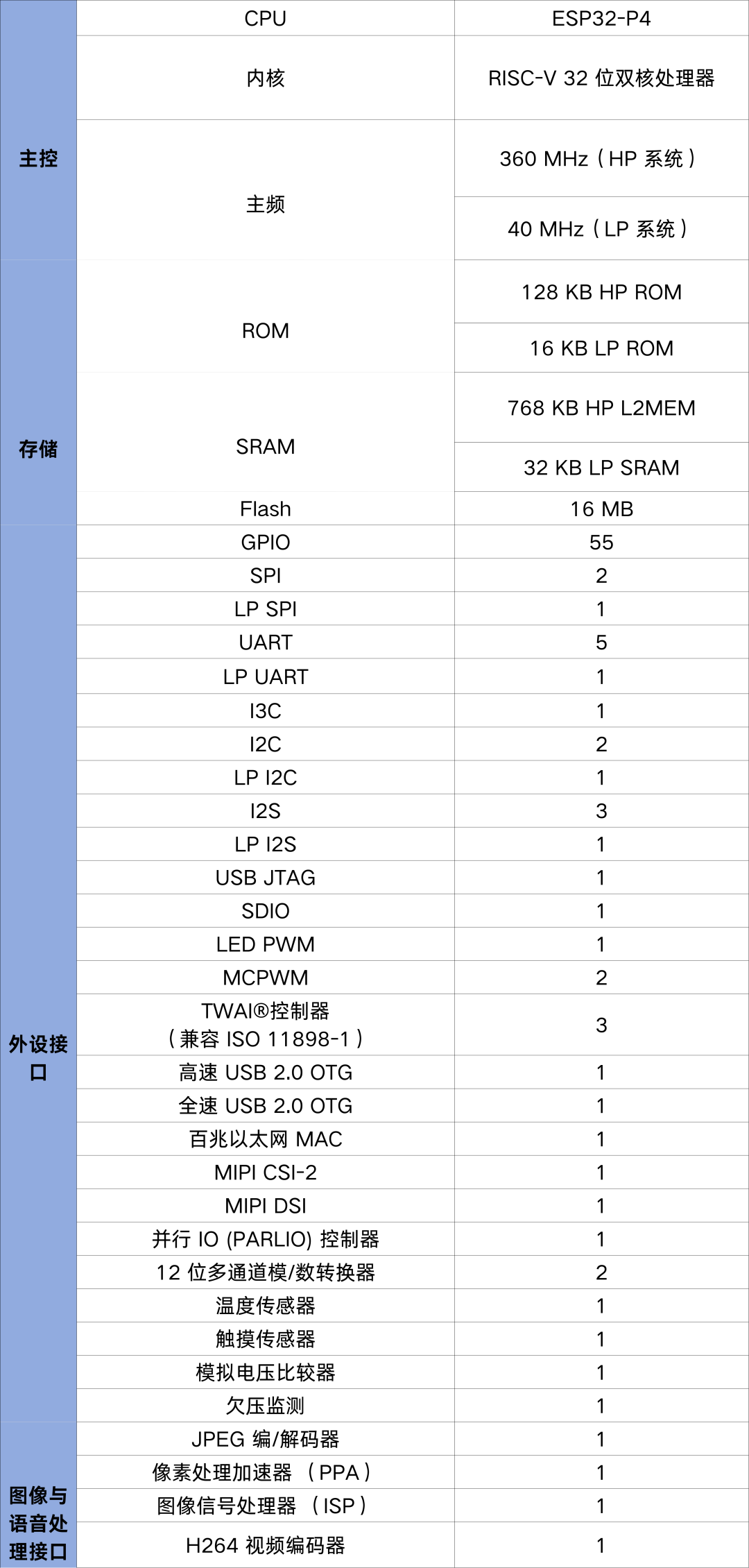

硬件参数

引脚定义

1

引脚布局

图7:引脚布局图

2

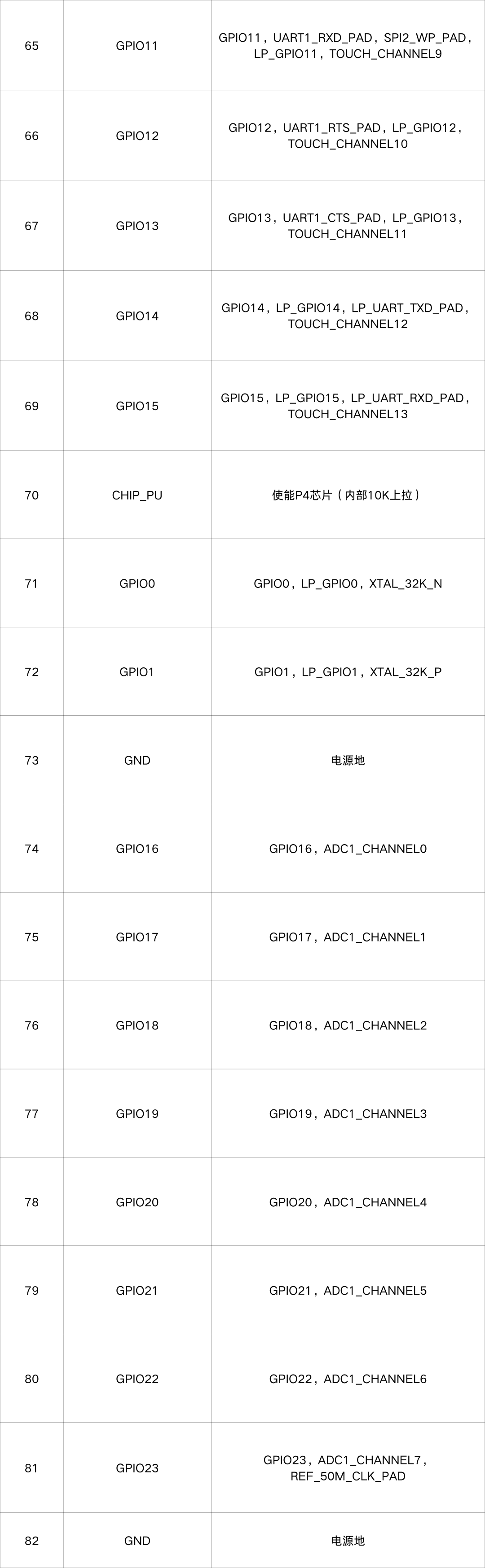

引脚描述

3

启动项配置

01

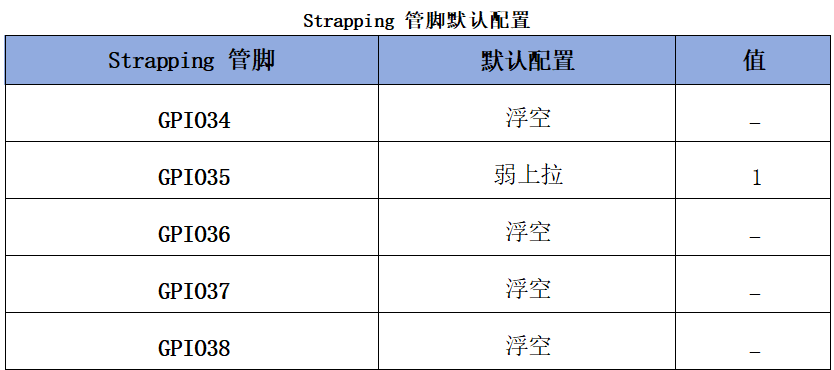

strapping 管脚

芯片在上电或硬件复位时,可以通过 Strapping 管脚和 eFuse 位配置如下启动参数,无需微处理器的参与:

芯片启动模式

Strapping 管脚:GPIO35,GPIO36,GPIO37,GPIO38

ROM 日志打印

Strapping 管脚:GPIO36

eFuse 位:EFUSE_UART_PRINT_CONTROL

JTAG 信号源

Strapping 管脚:GPIO34

eFuse 位:EFUSE_DIS_PAD_JTAG、EFUSE_DIS_USB_JTAG 和EFUSE_JTAG_SEL_ENABLE 上述 eFuse 位的默认值均为 0,也就是说没有烧写过。 eFuse 只能烧写一次,一旦烧写为 1,便不能恢复为 0。

上述 strapping 管脚如果没有连接任何电路或连接的电路处于高阻抗状态,则其默认值(即逻辑电平值)取决于管脚内部弱上拉/下拉电阻在复位时的状态。

要改变 strapping 管脚的值,可以连接外部下拉/上拉电阻。如果 ESP32-P4用作主机 MCU 的从设备,strapping 管脚的电平也可通过主机 MCU 控制。

所有 strapping 管脚都有锁存器。系统复位时,锁存器采样并存储相应

strapping 管脚的值,一直保持到芯片掉电或关闭。锁存器的状态无法用其他方式更改。因此,strapping 管脚的值在芯片工作时一直可读取,strapping 管脚在芯片复位后作为普通 IO 管脚使用。

02

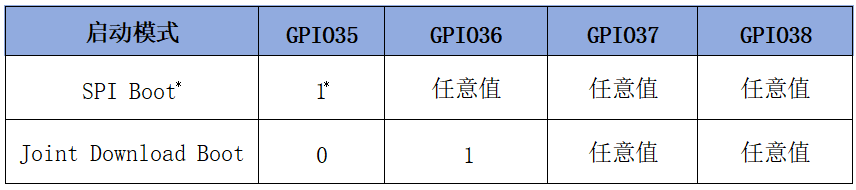

芯片启动模式控制

复位释放后,GPIO35 ~ GPOI38 共同决定启动模式。详见下表。

*表示默认值和默认配置。

Joint Download Boot 模式下支持以下下载方式:

USB Download Boot:

USB-Serial-JTAG Download Boot

USB 2.0 OTG Download Boot

2. UART Download Boot

SPI Slave Download Boot

03

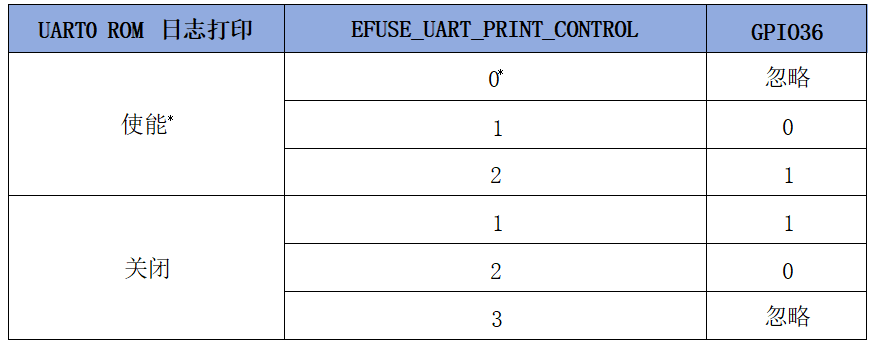

ROM 日志打印控制

系统启动过程中,ROM 代码日志可打印至:

(默认)UART0 和 USB 串口/JTAG 控制器

USB 串口/JTAG 控制器

UART0

EFUSE_UART_PRINT_CONTROL 和 GPIO36 控制 UART0 ROM 日志打印,详见下表

*表示默认值和默认配置。

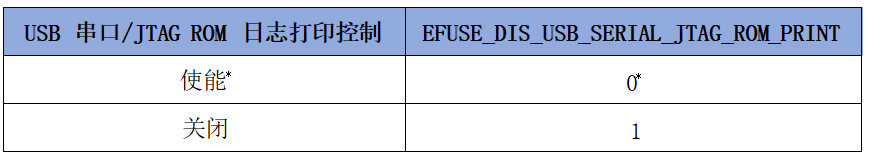

EFUSE_DIS_USB_SERIAL_JTAG_ROM_PRINT 控制 USB 串口/JTAG 控制器 ROM日志打印,详见下表。

*表示默认值和默认配置。

4. 电气特性

1

绝对最大限定值

超出绝对最大额定值可能导致器件永久性损坏。这只是强调的额定值,不涉及器件在这些或其它条件下超出本技术规格指标的功能性操作。长时间暴露在绝对最大额定条件下可能会影响 WT0132P4-A1 的可靠性。

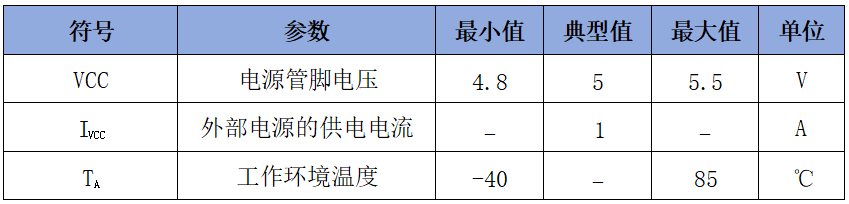

2

建议工作条件

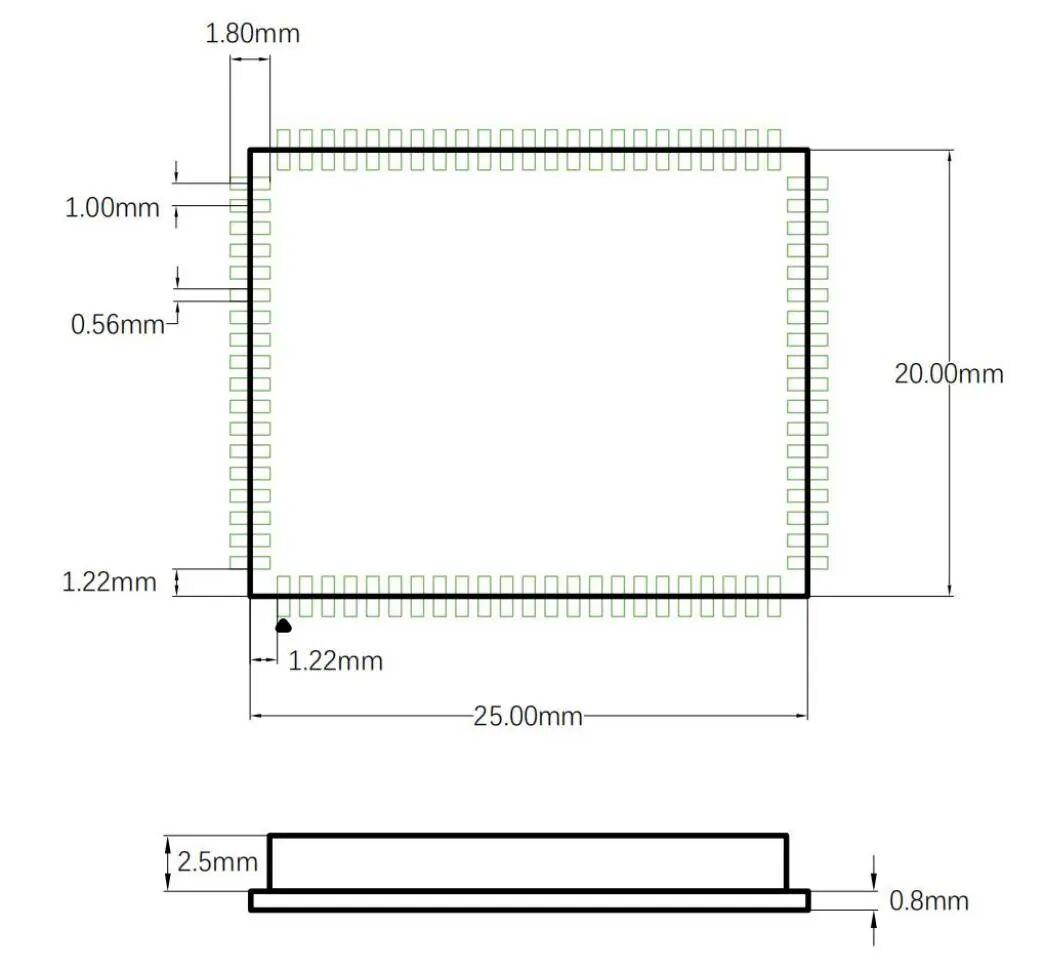

WT0132P4-A1 尺寸

下图为核心板的俯瞰图与正视图,公差±0.2 mm。

图9:WT0132P4-A1 尺寸图

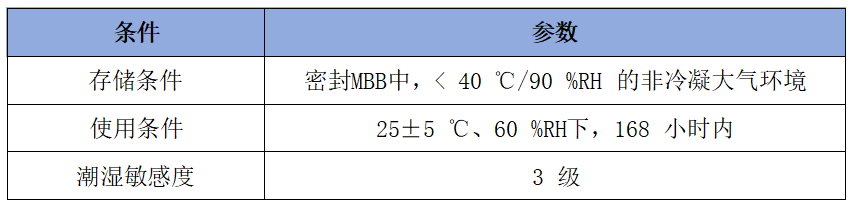

存储条件

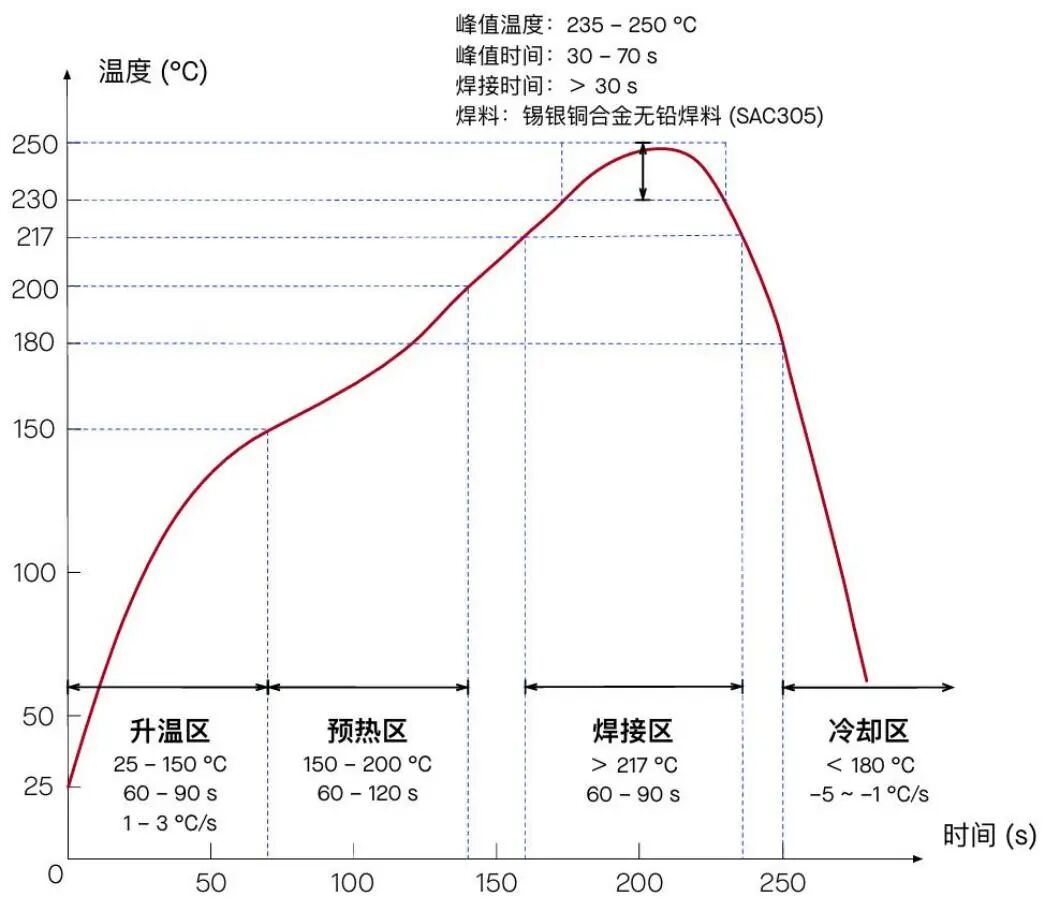

回流焊曲线

图10: 回流焊温度曲线图

推荐阅读: