SiC MOSFET具有导通电阻低、反向阻断特性好、热导率高、开关速度快等优势,在高功率、高频率应用领域中占有重要地位。然而,SiC MOSFET面临的一个关键挑战是降低特征导通电阻(RON,SP)与提升短路耐受时间(tSC)之间的权衡。以SiC MOSFET应用于半桥电路为例,当低侧的开关管开通时,高的dV/dt使高侧开关管栅压出现正向串扰,当该串扰电压高于阈值电压时,高侧开关管出现误开通,从而引发短路。此时的电源电压将瞬间加载在器件的漏极,与栅极电压共同作用,使器件处于高压大电流状态。虽然碳化硅材料的热导率更高,但由于SiC MOSFET的高功率密度使其在短路时具有更高的瞬时功率,局部高热将烧毁器件,使系统失效。

本文将系统地探究SiC MOSFET的短路鲁棒性,为器件制备工艺、设计、驱动的优化提供科学的指导依据,最终提升器件在实际应用中的鲁棒性和稳定性。

短路失效模式

SiC MOSFET的短路失效存在两种模式:

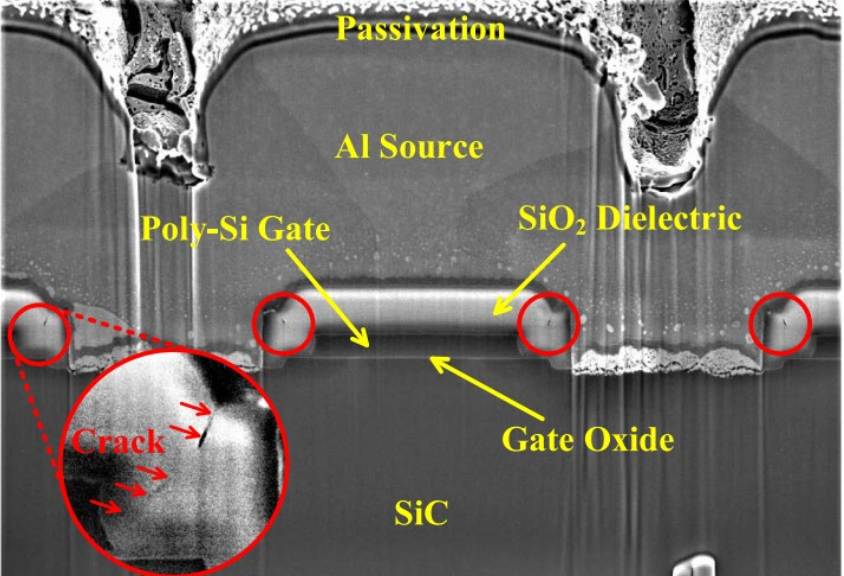

(1)由于材料之间的热膨胀系数不同,随着短路时间的增加,芯片结温升高,源极金属、层间介质、栅极Poly三层膜质会由于热膨胀而产生极大的应力,最终导致图一所示的层间介质层开裂。当高温使Al融化进入层间介质的裂缝后,就会引发栅源短路,最终使栅极损坏。这种模式下器件的体二极管通常保持完好,PN结仍保持阻断能力,因此不会对系统造成太大的损坏;

图一 SiC MOSFET短路失效模式——栅极损坏[1]

(2)随着短路时间的增加,芯片结温升高,芯片内部开始出现本征激发的热空穴,空穴电流激活了寄生NPN晶体管,进而发生热失控,电流剧增,如图二所示,芯片表面严重烧毁,融化的金属导致栅源漏三端短路,进而对系统造成损坏。

图二 SiC MOSFET短路失效模式——热失效[2]

实验平台介绍

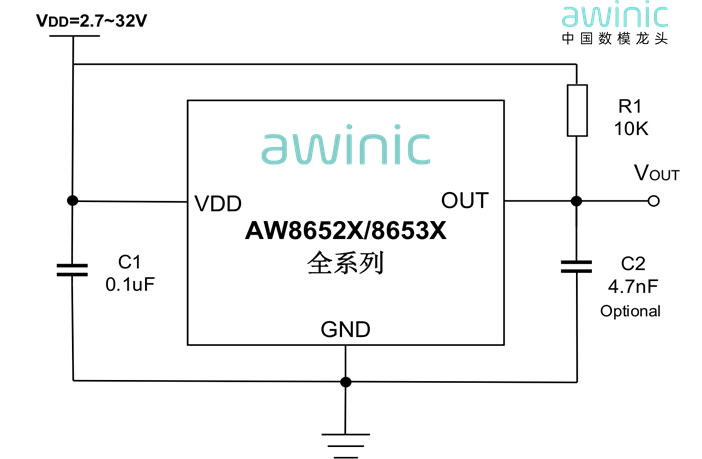

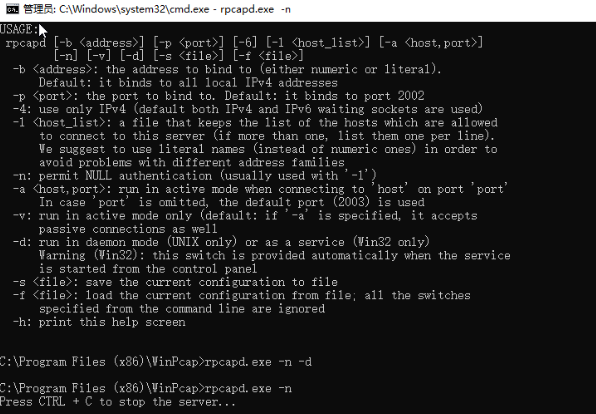

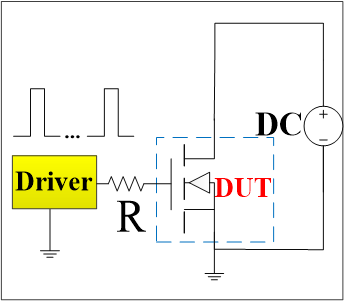

为了评估器件的短路鲁棒性,采用图三所示的短路测试电路拓扑测试:用导线将负载电源与待测器件直接连接,当栅脉冲处于低电平时,器件承受反向耐压VDD,当栅脉冲处于高电平时,器件开始导通,短时间内器件将流过电源电压的偏置条件下的饱和电流,它与电源电压一同作用于待测器件。实验中,通过逐步递增短路脉冲宽度的方式来测得器件的最大短路耐受时间。

图三 SiC MOSFET短路波形产生的电路拓扑结构

短路测试波形如图四所示:在短路过程的前半部分,栅压基本不变,但随着时间的增加,栅压开始慢慢下降。这是因为随着短路时间的增加,器件结温升高,栅极漏电增加,栅电阻开始降低,进而导致栅压降低。器件的电流随着栅极的开启迅速上升,直至饱和电流。达到饱和状态后,电流随着短路时间的增加逐渐降低。这是因为器件的结温升高,体电阻增加。其次,栅压降低,也会降低器件的导通电流。当短路时间进一步增加,器件的栅控能力降低,开始出现电流拖尾现象。最后,器件开始失效,彻底失去栅控能力[3]。

图四 SiC MOSFET承受不同时长的短路应力波形

提升短路鲁棒性方法

01器件制备端

优化栅氧氧化和钝化工艺,提升栅氧界面质量。在短路过程中,SiC MOSFET的栅氧化层承受较大的热应力,会导致栅极电流增加。因此,栅氧可靠性是提升短路鲁棒性的一个重要因素。

02器件设计端

①低器件饱和电流,日本三菱电机公司曾提出在源区引入一个更低掺杂的N+区,即串联了一个源极电阻,以降低短路电流,提升短路鲁棒性,但这牺牲了器件导通电阻[4]。

②增加沟道长度,避免电流集中在沟道区导致热烧毁。东南大学提出在MOSFET P阱区旁引入一个低浓度、浅结深的P区,等效增加了沟道长度,以减小沟道区的碰撞电离率,避免电流集中问题[5]。

③降低P阱区的电阻,抑制寄生晶体管的开启。增加P阱的掺杂浓度虽然可以降低P阱区电阻,但这会增加器件的阈值电压、降低器件的击穿电压。因此,美国纽约州立大学提出通过沟道注入技术形成深P阱,这降低了P区电阻,同时加强了JFET效应,新结构的饱和电流降低,短路能力提升了4倍[6]。

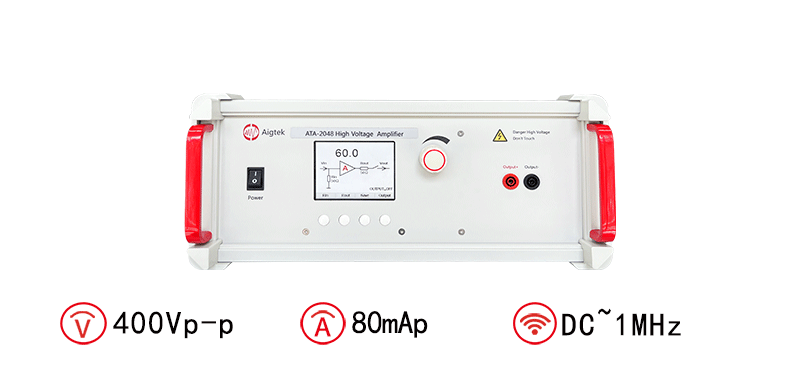

03电路驱动端

设置短路预保护机制,检测短路电流或器件两端电压,当短路电流/工作电压超过阈值后,驱动端降低栅极驱动电压,降低器件的饱和电流,进而延迟短路时间,为短路保护留足充分的启动时间。

结语

SiC MOSFET的短路可靠性核心挑战源于高电流密度引发的局部热积累和栅氧失效。在传统平面栅结构中,高温引起金属/介质层间/栅极Poly的热膨胀失配,导致层间介质开裂,最终栅源短路。此外,JFET区电流拥挤导致器件局部发热,进而触发寄生双极晶体管导通,最终引发热失效。这种高功率密度带来的热失效迫使平面栅采用牺牲导通特性的设计方案,这限制了其比导通电阻的进一步降低。为突破这一限制,沟槽栅结构通过消除JFET区来降低比导通电阻,但沟槽底部带来了栅氧电场集中问题,导致短路耐受时间缩短。为了提高沟槽MOS结构的短路鲁棒性,往往需要在槽底注入P屏蔽区或者采用双沟槽结构将电场往下拉,来降低槽底栅氧电场,但这同时也会带来短路时间和导通电阻的折中问题。对于3.3kV及以上高压,往往需要采用超结结构来降低器件的比导通电阻。然而,P柱的存在会影响短路期间电流的横向扩散,进而加剧局部温升,极大降低短路耐受时间,因此改善P柱布局、降低超结结构热阻系数是未来超结结构的一个重要研究方向。