在本篇文章我们将学习如何在 AMD VitisUnified 2024.2 中连接到 QEMU。 这是本系列的第 2 篇博文。要了解如何设置和使用 QEMU + 协同仿真,请参阅开发者分享|在 AMD Versal 自适应 SoC 上使用简单的 QEMU + 协同仿真示例。

创建 Vitis 工作空间

本篇文章使用的是 Vitis Unified 2024.2 来生成工作空间。此处使用的 XSA 与上一篇博客使用的相同。本文将创建一个“Empty Application”模板,并导入简单代码以测试 AXI GPIO。

您可遵循此处的教程,这些教程有助于您在 Vitis Unified IDE 中使用嵌入式流程:

https://github.com/Xilinx/Vitis-Tutorials/tree/2024.1/Embedded_Software/Getting_Started

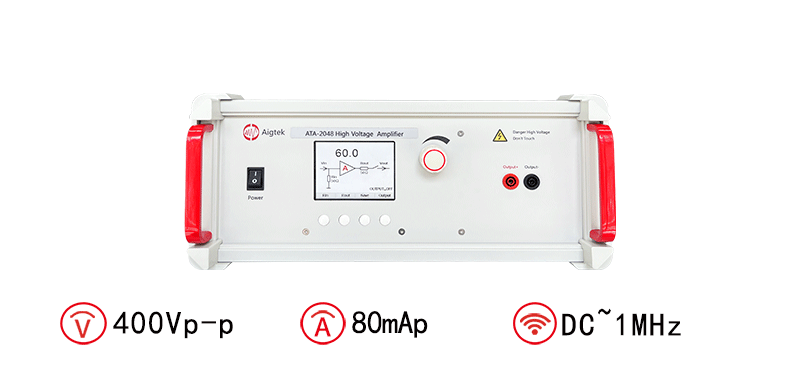

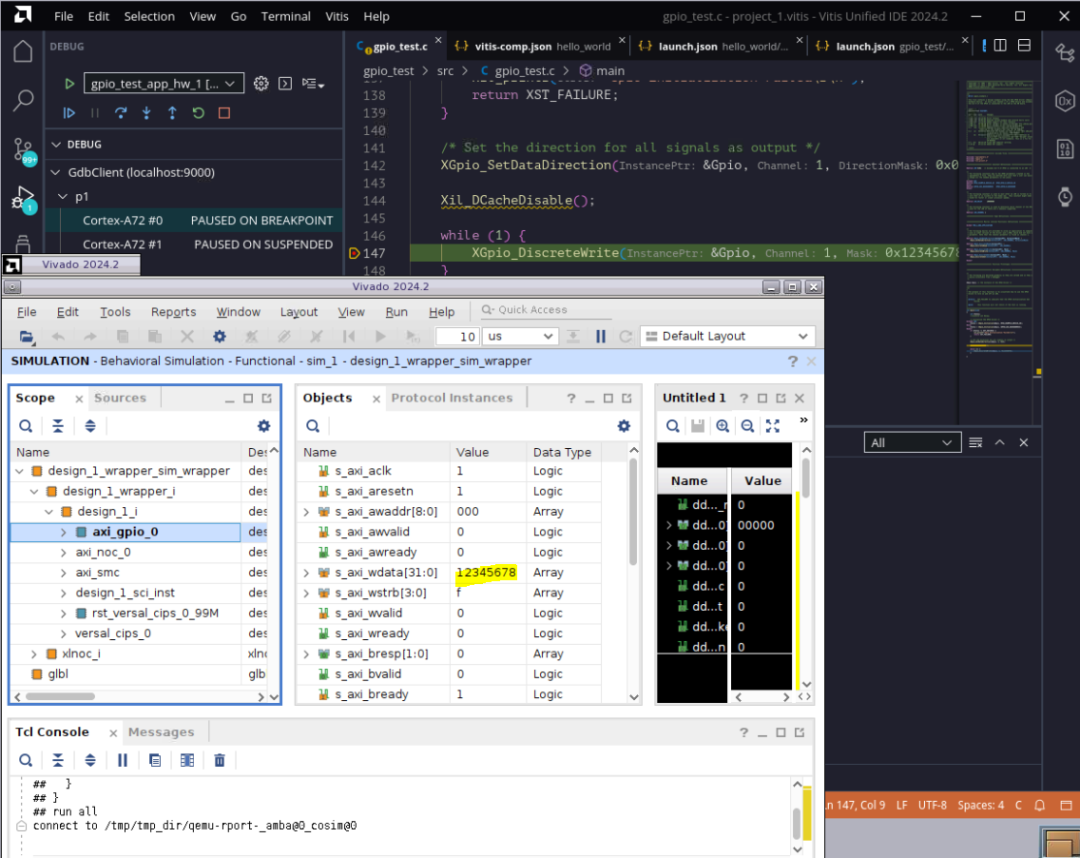

在本博客中已附上此处使用的代码。以下显示一段片段用于演示:

如您所见,只将 32 位值 0x12345678 写入 AXI GPIO 的数据寄存器。

连接 QEMU

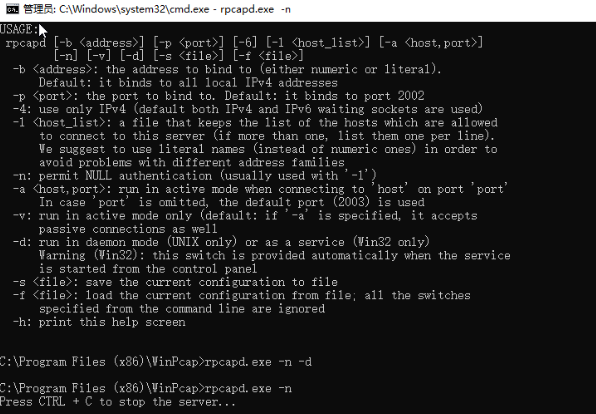

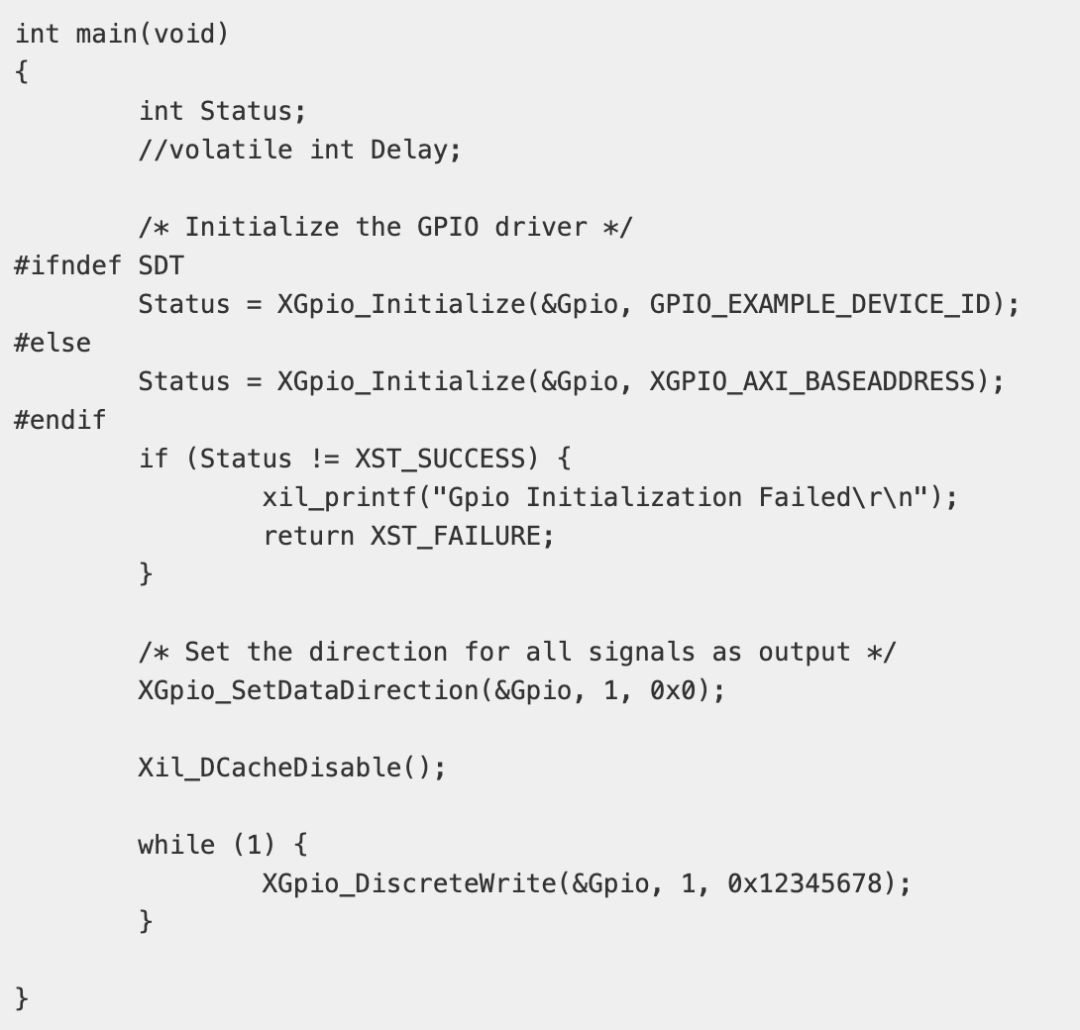

使用上一篇博客中的步骤启动 QEMU。用户可以留意 QEMU 中的 TCF 连接:

此处可以连接到 localhost 的端口 9000。

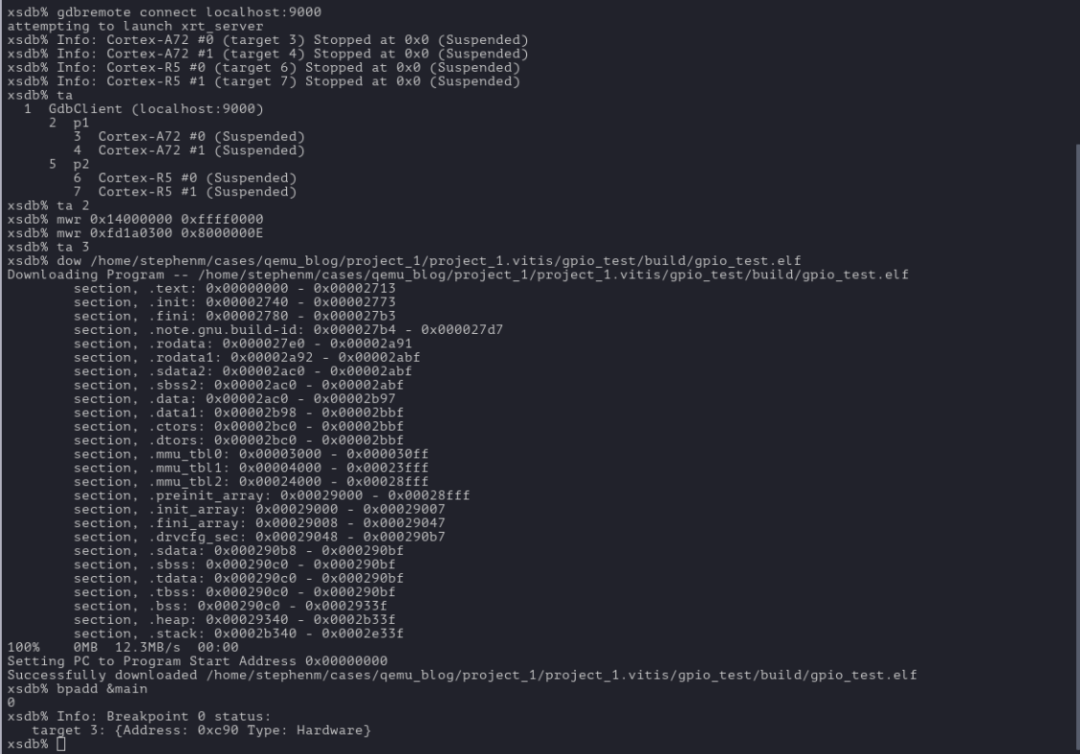

选择“Vitis -> XSDB Console”打开 XSDB 控制台,连接到 QEMU,并确保目标可见。

使用“connect -list”获取连接。我们需要使用此元数据连接到目标连接。

设置目标连接

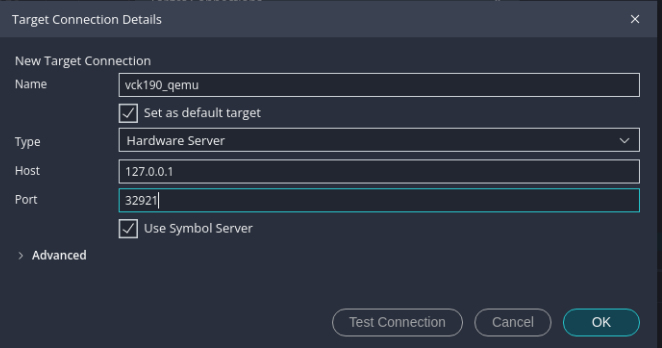

使用以上 connect -list 命令获取的端口搭配“Vitis -> Target Connections”中的 localhost (127.0.0.1)。

下载用户应用 ELF 文件

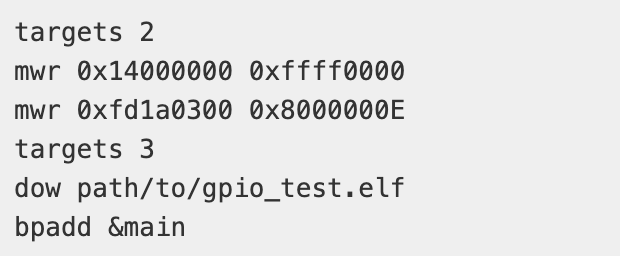

我们将连接到启动配置中运行中的目标。因此,需要手动下载 ELF,并将断点设置在 main() 处。并且,由于当前使用 PLM 来烧录器件,因此不存在对应 Cortex A72 的分区。因此,此处理器将保持置于复位。

我们需要使其解复位。在 OCM 中放置一个启动循环 (0x14)。

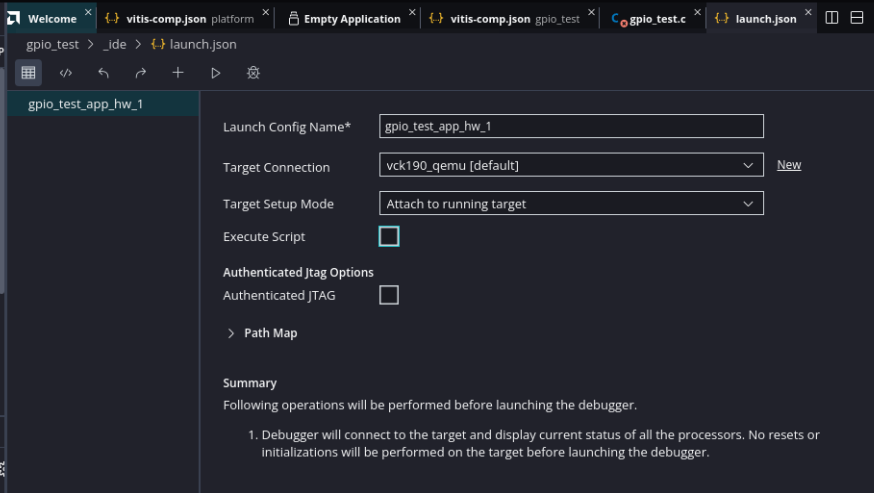

设置启动配置

我将连接到以上创建的目标连接,并将“Target Setup Mode”设置为“Attach to running target”。

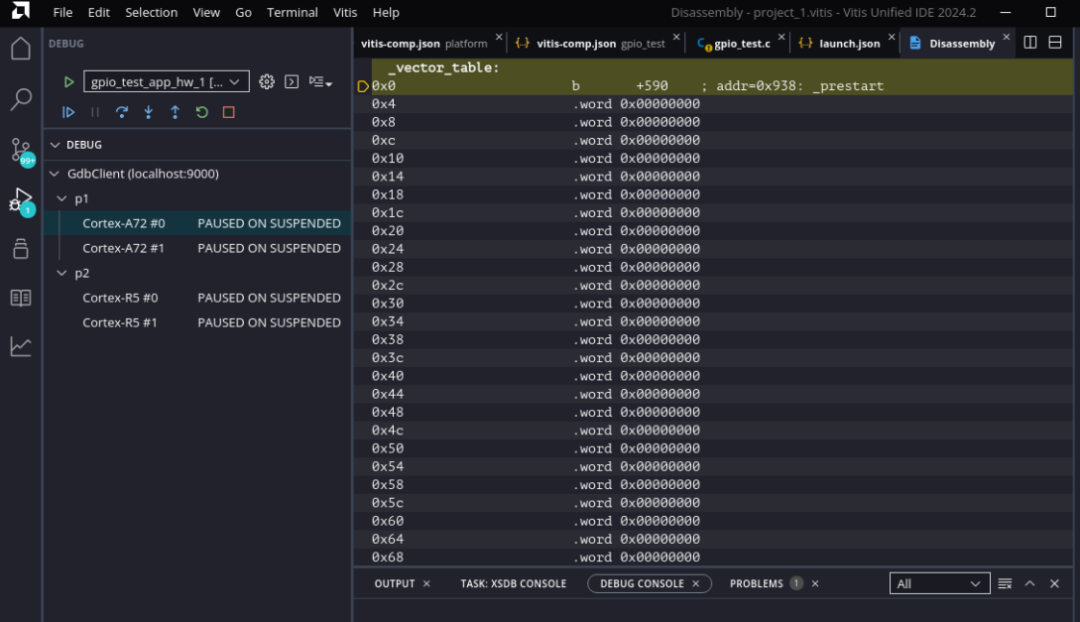

这将跳转至调试透视图。由于我们尚未命中位于 Main 处的断点,因此您将看到启动代码。

注释:请确保您高亮正确的目标,因为它可能已切换到不同的处理器目标。

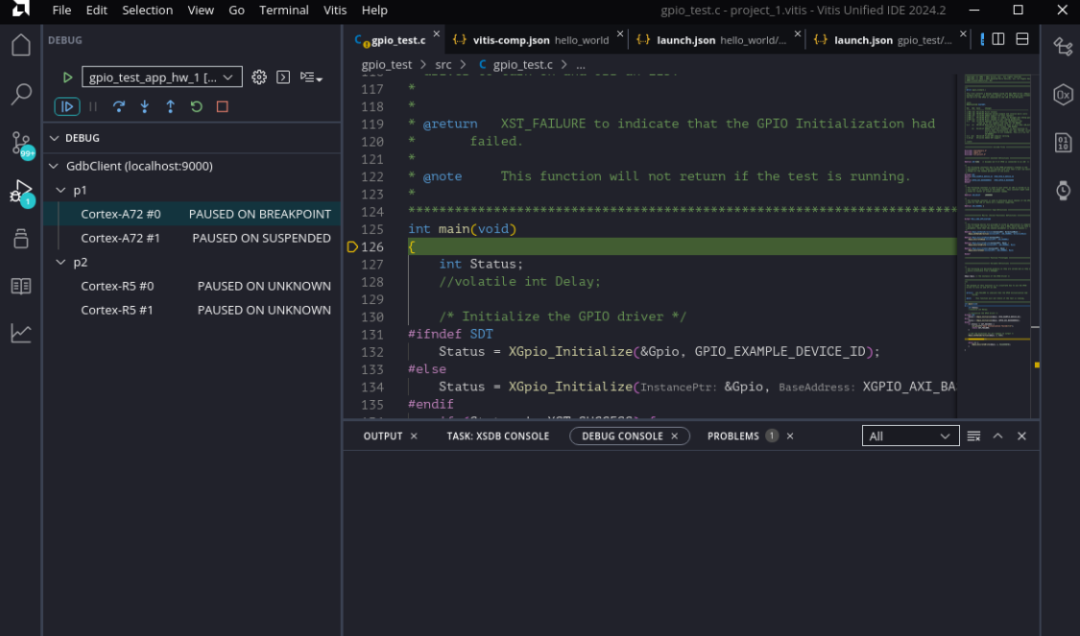

如果您点击“Continue”,那么应该会命中位于 main() 处的断点。

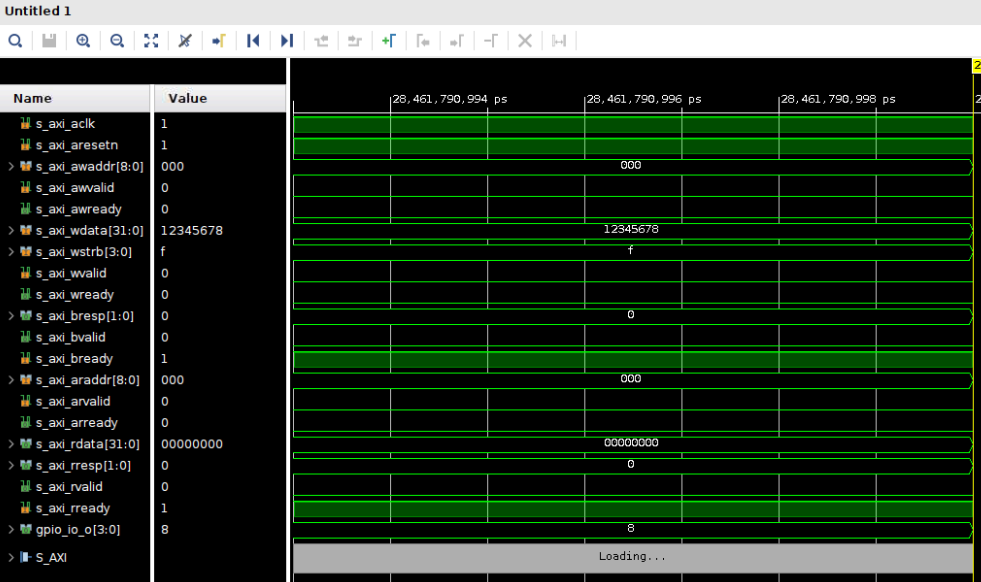

如果在 While 循环中设置断点以写入 AXI GPIO,即可在 AMD VivadoDesign Suite 仿真器中的 WDATA 管脚上看到传输事务:

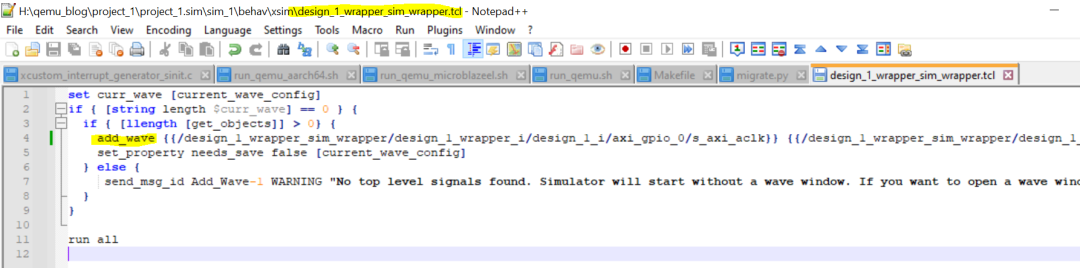

注释:如果您想要将更多其他信号添加到波形图中,可以更新仿真目录中的 Tcl 文件。

例如,在此处添加了 AXI GPIO 接口信号:

如果重新运行应用代码,即可在这些端口上看到所期望的如下输出: